【导读】在冶金行业中,很多控制信息的传递都是在总线的基础上进行的,通过总线能够实现对各个生产加工环节的实时监控,总线技术随处可见,其中VME计算机因其支持多个CPU,64位的寻址和数据传输能力,IEC 297 欧卡标准,机械性能可靠和稳定,并具有可靠的接插件,带电热插拔,多厂商支持等优点得到广泛应用。这里介绍一个用双口RAM实现变频器和VME通讯的实际例子。

1、总体结构

如图所示,整个通讯由三部分组成:DSP,VME双口RAM。

图1:系统结构图

1.1 DSP部分

这部分是整个电机控制系统的核心。DSP主要被用来产生控制电机的PWM脉冲,本项目使用的芯片是德州仪器的TMS320LF2407A芯片,它内部有两个事件管理器,可以最多生成12路脉冲信号;集成了高性能的10位ADC、SCI、SPI、CAN等模块,真正实现了单芯片控制,性能稳定,功能强大。

1.2 VME总线

VME总线,Motorola公司1981年推出的32位工业开放标准总线,主要应用于工业控制现场,实现数据的高速采集,总线上设备之间的实时通讯等。 VME总线的插板一般有两种尺寸,一种是3U高度的带一个总线接口J1,另一种是6U高度的带2个总线接口J1、J2。一般每块VME总线的插板上的接口 J1、J2都有96针,每一个接口都是3排,按A、B、C排列,每排32针,J1一般用于直接与VME总线相连,J2的中间列用于扩展地址总线或数据总线,另外两列可由用户定义及I/O、磁盘驱动及其他外设等。

1.3 双口RAM

双口RAM具有两套完全独立的数据线、地址线、读/写控制线,允许两个CPU对双端口存储器的同一单元进行同时存取;具有两套完全独立的中断逻辑来实现两个CPU之间的握手控制信号;具有两套独立的“忙”逻辑,保证两个CPU同时对同一单元进行读/写操作的正确性;兼容性强,读/写时序与普通单端口存储器完全一样,存取速度完全满足各种CPU的要求。这些特点使得双口RAM能够胜任一些要求高速度,实时通讯的场合。 双口RAM有两套相互独立的存储电路,两者通过控制仲裁电路相互连接。以IDT7024为例,该芯片是4K*16的静态存储器,典型功耗750mW,最大存取时间有15/17/20/25/35/55ns,可采用中断、忙逻辑、旗语三种方式来协调信息交换的双方。

2、硬件组成

2.1 DSP部分

使用TMS320LF2407A芯片,为了和双口RAM 连接,应将DSP的16位数据线和12位地址线引出,另外还有控制信号线:DS、R/W。

2.2 VME总线

这里使用VMIC公司的标准6U机箱,含J1,J2两个总线接口,只使用J1进行通讯。

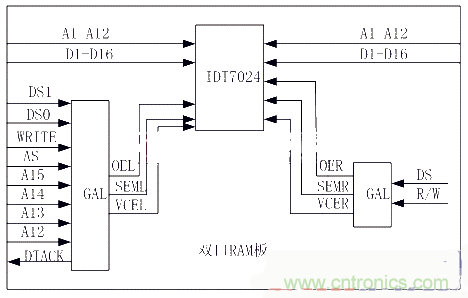

2.3 双口RAM

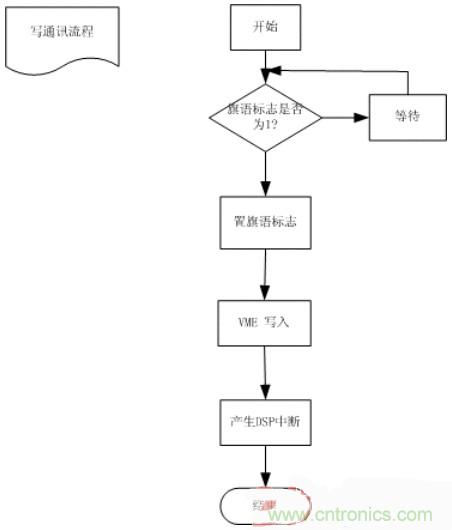

双口RAM有两套相互独立的地址和数据线,将它们分别和DSP、VME总线的地址和数据线相连,并把J1和DSP的控制信号线连到GAL上面,对双口 RAM进行逻辑控制,如下图所示: 3 通讯流程 这里我们把VME作为主设备,DSP作为从设备,DSP的读写操作都受到VME的控制。需要注意的是,对同一个地址不能同时写或者一边写一边读,防止产生写入和读取错误的数据,以下分别是读写通讯的流程图:

图2:流程图

如果VME向双口RAM中“写入”数据,首先需要判断写入数据的区域有没有正在被DSP端“读”或者“写”,可以通过“旗语标志位”进行判断,判断DSP 并没有对该区域进行操作的时候,VME获得该区域的控制权,并置“旗语标志位”。写完数据,VME向DSP端的中断标志位写入数据,这样,双口RAM便会产生DSP中断信号,提示DSP读取数据。

图3:电路图

如果VME从双口RAM中“读”数据,首先需要判断读数据的区域有没有正在被DSP端“写”,可以通过“旗语标志位”进行判断,判断DSP并没有对该区域进行操作的时候,VME就可以从该区域读取数据。

相关阅读:

国内现行轨道交通安全门系统驱动电机控制方案

网友分享:基于Arduino的直流电机控制