【导读】本文设计了一种高增益低噪声的探测器读出电路,采用CTIA 与CDS 电路相结合,通过对CTIA 电路中积分电容的改进,使电路在宽范围内对微弱信号读出,并采用开关控制和CDS 电路来降低噪声,使电路信噪比达到10,该电路对航空航天领域微光探测系统读出电路的设计具有重要意义。

当前固体微光器件以EBCCD 及EMCCD 器件为主,随着CMOS 工艺及电路设计技术的发展, 微光CMOS 图像传感器的性能在不断提高,通过采用专项技术,微光CMOS 图像传感器的性能已接近EMCCD 的性能, 揭开了CMOS 图像传感器在微光领域应用的序幕。随着对微光CMOS 图像传感器研究的进一步深入,在不远的未来,微光CMOS图像传感器的性能将达到夜视应用要求,在微光器件领域占据重要地位。

读出电路是微光CMOS 图像传感器的重要组成部分,它的基本功能是将探测器微弱的电流、电压或电阻变化转换成后续信号处理电路可以处理的电信号,它的噪声水平限制着CMOS 图像传感器在微光下的应用。微光条件下像素的输出信号十分微弱,任何过大的电路噪声、偏移都可以将信号湮没,因此提高读出电路输出信号的SNR 是微光设计的关键之一。本文采用的新型电容反馈跨阻放大型读出电路CTIA电路,可以提供很低的探测器输入阻抗和恒定的探测器偏置电压,在从很低到很高的背景范围内,都具有非常低的噪声,其输出信号的线性度和均匀性也很好,适合微弱信号的读出。

1 电路设计

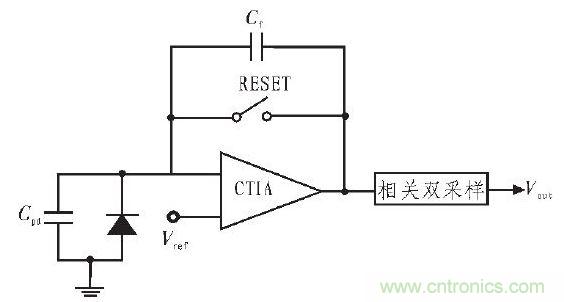

为完成探测器输出电流向电压的精确转化,所设计的电路由CTIA 和相关双采样(CDS)组成,CTIA 由反向放大器和反馈积分电容构成的一种复位积分器。其增益大小由积分电容确定。图1 为典型CTIA 电路结构。

图1 典型CTIA 结构

当Reset 信号为高时,MOS 开关开通,由运算放大器的虚短特性可知,输入端的电压与Vref相等,此时积分电容两端电压相等, 都为Vref。当Reset 信号变为低电平时,MOS 开关关断,由于输入端的电压由Vref控制,因此在积分电容Cf右极板上产生感应电荷并慢慢积累,右极板电压逐渐增大,积分过程开始。最后电压通过相关双采样电路读出。

2 关键单元电路设计

2.1 高增益低噪声CTIA电路

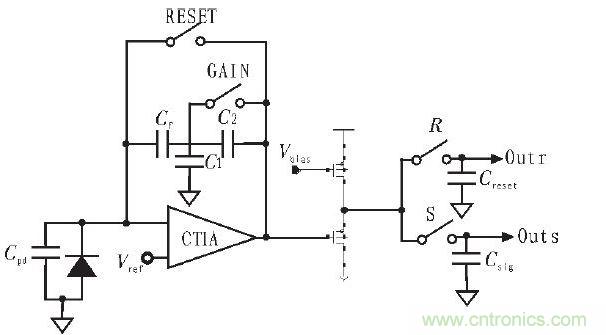

为了提高读出电路的增益,使电路能在比较短的积分时间内,读出PA 级的电流,电路中的积分电容要非常小。同时为了提高信噪比,在减小积分电容的同时,电路噪声也要减小。在新型电路结构中,采用T 型网络电容加nmos 开关,电路结构如图2 所示。

图2 高增益低噪声CTIA电路

由于C1和C2的作用, 使得Cf在CTIA 反馈回路中的有效值减少,其有效值为:Cfb= ( C2Cf)/(Cf +C1+C2),这样Cf可以取相对较大的值,避免了使用小电容,因为小电容在工艺上较难实现,且误差较大。在本电路中,Cf=20 fF,C2=18 fF,C1=150 fF,则Cfb=2 fF。

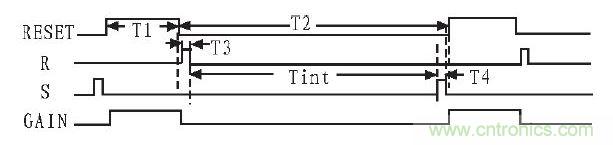

图3 为该电路的工作时序。

图3 高增益低噪声CTIA 电路工作时序

该电路可工作在高增益模式或低增益模式。在高增益模式, 当reset 为高电平时,gaIn 导通, 这时有效电容为Cf,当reset 为低电平时,gaIn 关断, 此时的积分电容为Cf、C1和C2组成的T 型网络电容, 这样保证了电路在复位时大电容,可有效降低噪声,积分时小电容,可大大提高增益。当gaIn 一直为高电平时,电路工作在低增益模式。

2.2 相关双采样

相关双采样电路由两组电容和开关组成,电路工作过程如下。首先,开始积分,R 导通,相关双采样电路先读出像素的复位信号,存储Vreset电压到电容Creset中。积分完成,开关S导通,将电压Vread储存到电容Csig中。最后,将存储在两个电容之上的电压值相减得到最终的像素输出电压值:

Vout=Vouts -Voutr

这种结构可以很好的消除CMOS 图像传感器中像素的复位噪声、1/f 噪声以及像素内的固定模式噪声。

[page]

3 噪声分析

CMOS 读出电路中包括光探测器、MOS管和电容3种元件。光探测器和MOS管是读出电路的主要噪声源,这些噪声包括:一方面光探测器和MOS 管的固有噪声;另一方面由读出电路结构和工作方式引起的噪声。

3.1 光探测器噪声

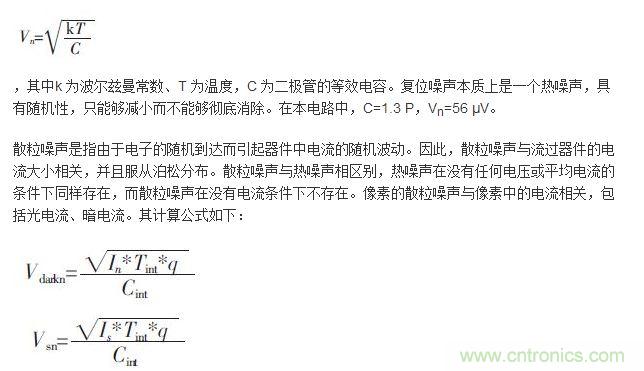

复位噪声是由复位管引入的一种随机噪声。当像素进行复位时,复位管处于饱和区或亚阈值区,具体状态取决于光电二极管的电压值。复位管导通时可以等效为一个电阻,而电阻存在的热噪声将引入到复位信号形成复位噪声。其大小与二极管的电容有关,复位噪声电压为

光电流散粒噪声与照度有关,很难消除。与暗电流有关的散粒噪声可以通过改变掺杂浓度减小暗电流,但这会降低量子效率。在本电路中,In=100 fA,Is=20 pA,Tint=20 μs,C int =2 fF,则Vdarkn=0.28 mV,Vsn=4 mV。

3.2 读出电路噪声

闪烁噪声也称为1/f 噪声。在半导体材料中,晶体缺陷和杂质的存在会产生陷阱, 陷阱随机捕获或释放载流子形成闪烁噪声。在读出电路中,CTIA 放大器是闪烁噪声的主要来源。

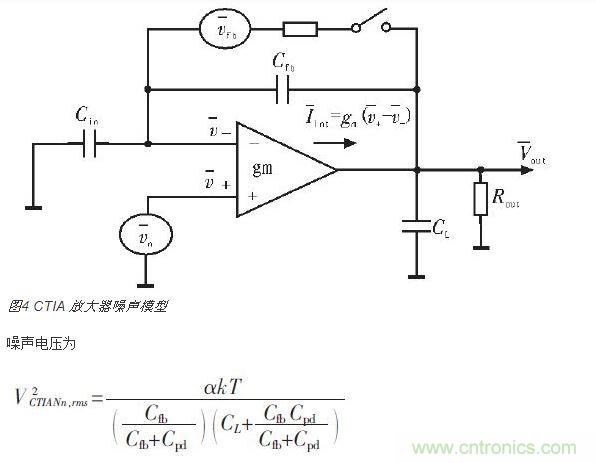

CTIA 读出噪声与输入端电容Cin=Cpd、反馈电容Cfb,以及负载电容CL的设计均有关,其小信号噪声模型如图4 所示。

在本电路中,Cfb=2 fF,Cpd=1.3 pF,CL=1 pf,α=1.5,T=300 K,则Vn=2 mV。

3.3 固定模式噪声(FPN)

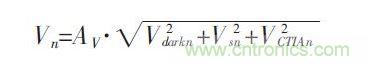

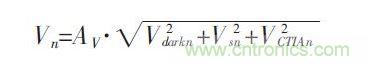

之所以称为固定模式噪声,是因为这种噪声产生的影响不随时间的变化而变化,即表现在每帧图像上的误差是一致的。像素的固定模式噪声可以通过读出电路中的相关双采样电路进行消除。通过以上分析,在本电路中,噪声的主要来源在于光探测器的散粒噪声和CTIA 放大器的闪烁噪声, 输出总噪声为

噪声电压为

6

其中:Av为输出跟随放大器增益0.7。

根据公式,理论计算噪声电压Vn=3.1 mV,实际电路的噪声水平会比理论值大2 倍左右。

[page]

4 仿真与测试结果

4.1 电路版图和仿真结果

本文所设计的电路采用CSMC 公司0.5 μm CMOS 工艺模型,对电路进行Spectre 仿真、版图设计和流片。

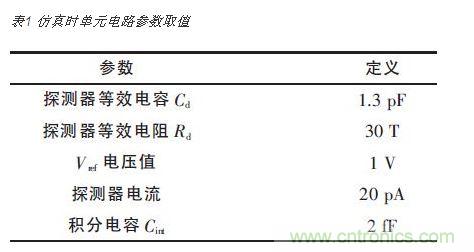

表1 是对探测器进行的参数设置,主要依据的是相应材料制作的探测器对应测试得到的等效电阻值和等效电容值以及探测器流过的光生电流来确定的, 其中Vref是外加在放大器正相端的电压值。

表1 仿真时单元电路参数取值

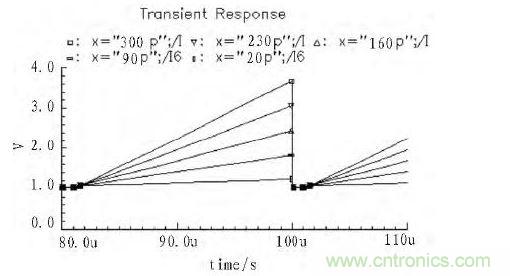

图5 CTIA 输出的仿真波形。

图5 CTIA 输出波形

从图5 可看出,当信号电流为20 pA 时,电路输出差分电压为90 mV,根据噪声电压的估算值,最小信号的信噪比SNR=15。

4.2 测试结果

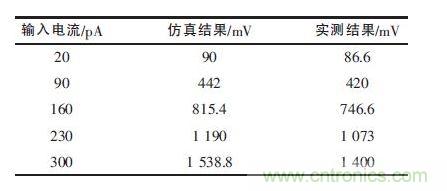

采用CSMC 公司的0.5 μm 标准CMOS 工艺库对电路进行流片,表2 为仿真结果和实际测试结果比较(Cf=20 fF,C1=150 fF,C2=18 fF 信号输入20~300 pA,积分时间20 μs)。

表2 仿真结果和实际测试结果比较

从表2 可以看出,实测结果略小于仿真结果,当光信号为20 pA 时,测得电路噪声电压为8 mV,则SNR=10.8。