【导读】运放同相和反相端输入电压超过运放共模输入电压的范围,就会导致输出电压异常,达不到预期电路的设计范围。关于运放的两个输入引脚有输入摆幅限制,只要是由于输入极的设计导致的。

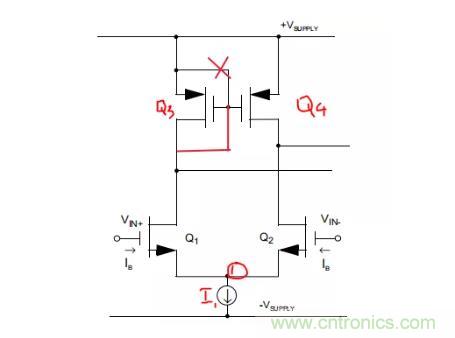

运放同相和反相端输入电压超过运放共模输入电压的范围,就会导致输出电压异常,达不到预期电路的设计范围。关于运放的两个输入引脚有输入摆幅限制,只要是由于输入极的设计导致的。运放的输入极基本是CMOS,BJT和FET三种基本拓扑结构组成的,下面用CMOS输入极的拓扑结构来做说明,参考资料来自MICROCHIP的AN722A的应用文章,会作为附件上传,图示是一个NMOS输入极,一共用到了四个MOS管。但是其中给出内部示例图还有错误,所以网络的资料也不能完全相信,需要自己做争取的判断。图中Q3和Q4作为镜像电流源,给Q1和Q2的差分对管提供直流静态工作点的电流。但是原图把Q3的GS短接到一起,这种连接的方式明显是错误的,应该是Q3的GD连接,让VGS=VDS,让Q3管始终工作在饱和区。

说到了饱和区,就有了判定条件的。图中四个MOS管都需要工作在饱和区,才能实现信号的放大。单个MOS管的本征放大倍数A=gm*ro,接入不同的外围电路,可以实现不同的放大倍数。

按照AN-00722A中表述,对于这个差分输入对,输入共模电压的范围将被限制在负电源电压附近,在这种情况下,输入端的电压最高可高于正电源轨的十分之几伏,但最低只能降低到高于负电源轨的1.2V处,用不等式表示如下:

Vss+1.2<Vcom<Vcc+0.3

其中Vss表示负电源轨,Vcc表示正电源轨,高于正电源轨的十分之几伏定义为0.3V;

但是在应用手册中没有对这个过程做解释说明,后来查了一些资料,对这个过程有了理解,所以分享到大家。

从电路可知,还有一个电流源I1,可以理解为一个简单的constant current(也可以是cascode current),就是一个MOS管工作的饱和区的模式,那么可以定义1点和Vss之间的电压V1-Vss=0.3V,也就是constant current的漏极和源极之间的压降是0.3V。

随后定义Q1到Q4四个MOS管工作在饱和区Vgs≥0.9V(Vgs(th)), 即Vgs-Vgs(th)≥0 这个根据不同半导体厂家的定义会不同,但是0.9的设计是可以实现的。

由于Q3的栅极和漏极连接到一起,定义Vgs3=Vds3=0.6V,至此所有已知条件都有了,可以进行计算。

对于Q1要保证可以开启,所以栅源极电压至少要大于0.9V,

Vgs1=Vin-V1≥0.0V

Vin-(0.3+Vss)≥0.9V

Vin≥Vss+1.2

对于Q1不仅要开启还要工作在饱和区,所以Vds1≥Vgs1-Vgs(th)

Vgs1=Vin-(0.3+Vss)

Vgs(th)=0.9V

Vd1=Vcc-Vds3

Vs1=0.3+Vs

Vds1=Vcc-0.6-(0.3+Vs)

将以上所有式子联立可得到

Vin≤Vcc+0.3

根据以上求得的所有关系式,就可以得到输入共模电压的范围:Vss+1.2<Vcom<Vcc+0.3这个和资料上给出的是完全一致的。

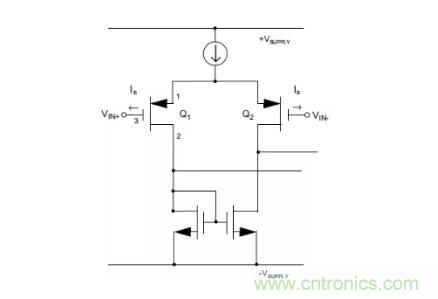

既然有NMOS输入极,那就肯定有PMOS输入极,无非就是NMOS和PMOS进行调换的,如下图所示:

有了上面求解的过程,过于PMOS的输入共模电压范围就不做详细分析,可以直接拿出结论,对于Q1需要工作在饱和区,因此就有:

Vcc-0.3-(VCC+0.6)≥Vcc-0.3-Vin-0.9

Vin≥Vcc-0.3

对于Q1需要先正常开启,因此就有

Vcc+0.3-Vin≥0.9

Vin≤Vcc-1.2

整合以上的式子,就可以得到PMOS输入共模电压范围:Vcc-0.3≤Vin≤Vcc-1.2

和手册上提到的,输入端无法在器件离开线性区之前比正电源电压高几百个毫伏以上的结论是想吻合的。

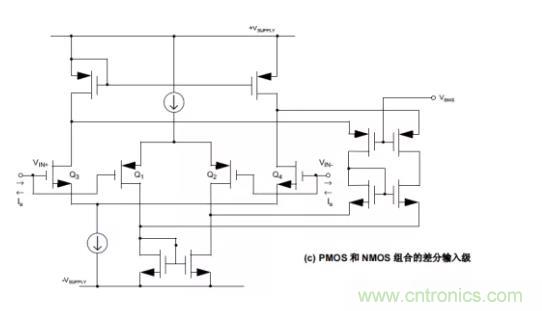

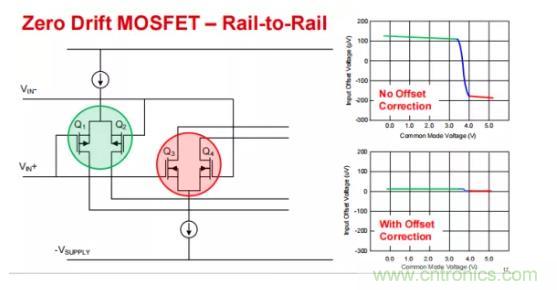

从推导结果看来,无论是NMOS输入极还是PMOS输入极,都不是轨对轨的运放。但在我们实际应用中,很多运算放大器都是轨对轨,这个时候就是PMOS和NMOS的组合管输入极,毕竟从结果看来,NMOS输入极是正电源轨输出,PMOS是负电源轨输出。采用组合管输入极,可以有效的讲P管和N管的优点结合起来,就能保证正负电源轨同时输出。示意图如下图所示:

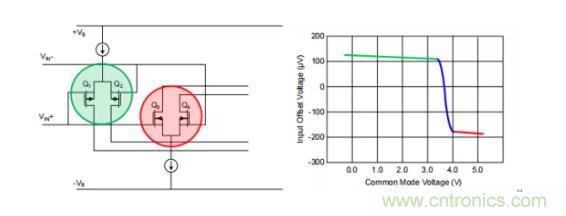

电路看起来比较复杂,实际就是两个输入极的叠加组合。现在知道了工作原理,以后和运放的内部框图,就能看出运放是不是轨对轨输出了。但是这种形式的输入极还是有一些不好的地方,比如失调电压的范围比较宽。从TI给出的仿真结果来看,对于OPA703这个运放,尽管是轨对轨输出,但是失调电压的动态范围受到共模输入电压的影响,动态变化很大,实际使用的时候回受到很多制约的。

所以在此基础上,就需要对P管和N管互补输入极的电路进行改进,半导体公司就设计出了0偏移的MOS管轨对轨技术,有效改善了失调电压变化范围大的问题。所以在设计电路的时候,要根据系统的设计需求,选择合适争取的运放,即使都是轨对轨运放,性能还是有很大的不同。只要性能参数选择争取,才能满足电路的要求。

确实有很多资料介绍了运放共模输入电压限制的结论,但是对这个过程没做说明,这个帖子对这个过程做了一定的解释和说明,感兴趣的一起讨论哈!

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请电话或者邮箱联系小编进行侵删。