机遇与挑战:

- TSV 3D IC技术发展速度相当缓慢

- TSV 3D IC面临诸多挑战

- 2016年将完成多种半导体异质整合水平

TSV 3D IC技术虽早于2002年由IBM所提出,然而,在前后段IC制造技术水准皆尚未成熟情况下,TSV 3D IC技术发展速度可说是相当缓慢,DIGITIMES Research分析师柴焕欣分析,直至2007年东芝(Toshiba)将镜头与CMOS Image Sensor以TSV 3D IC技术加以堆栈推出体积更小的镜头模块后,才正式揭开TSV 3D IC实用化的序幕。

于此同时,全球主要芯片制造商制程技术先后跨入奈米级制程后,各厂商亦警觉到除微缩制程技术将面临物理极限的挑战外,研发时间与研发成本亦将随制程技术的进步而上扬,因此,包括IBM、三星电子(Samsung Electronics)、台积电(TSMC)、英特尔(Intel)、尔必达(Elpida)等芯片制造商皆先后投入TSV 3D IC技术研发。

至2011年第4季,三星与尔必达分别推出采TSV 3D IC同质整合技术高容量DRAM模块产品,并已进入送样阶段,台积电则以28奈米制程采半导体中介层(Interposer)2.5D技术为赛灵思(Xilinx)制作出新一代现场可程序逻辑门阵列(Field Programmable Gate Array;FBGA)产品。

然而,柴焕欣说明,各主要投入TSV 3D IC半导体大厂除面对晶圆薄型化、芯片堆栈、散热处理等相关技术层面的问题外,随TSV 3D IC技术持续演进并逐渐导入实际制造过程中,前段与后段IC制程皆出现更多隐藏于制造细节上的问题。

加上就整体产业链亦存在从材料、设计,乃至生产程序都尚未订出共通标准,而晶圆代工业者与封装测试业者亦无法于制程上成功衔接与汇整,都将是造成延误TSV 3D IC技术发展与市场快速起飞重要原因。

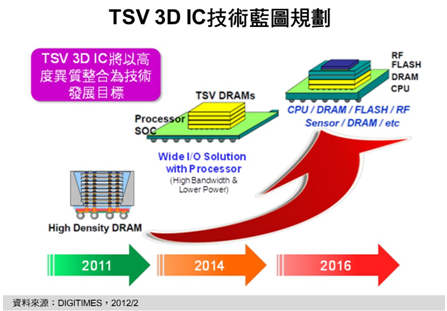

综合各主要芯片制造商技术蓝图规画,2011年TSV 3D IC是以同质整合的高容量DRAM产品为主,至2014年,除将以多颗DRAM堆栈外,尚会整合一颗中央处理器或应用处理器的异质整合产品。柴焕欣也预估,要至2016年,才有机会达到将DRAM、RF、NAND Flash、CPU等各种不同的半导体组件以TSV 3D IC技术整合于同1颗IC之中异质整合水平。