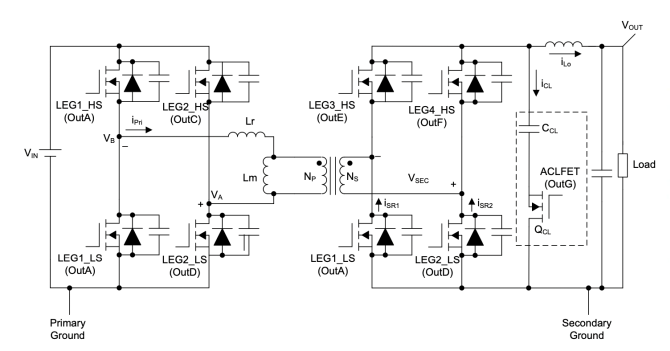

【导读】相移全桥(PSFB)转换器因其能在初级侧开关管上实现软开关(降低开关损耗),成为高功率应用(如服务器电源、工业电源、通信电源)的主流拓扑。然而,传统的PSFB存在一个显著痛点:变压器漏感(Lr)与输出整流器(特别是同步整流管MOSFET)的寄生电容(Coss)谐振,会导致次级侧产生严重的电压振铃和尖峰。此尖峰电压理论上可达 2 × VIN × (NS/NP),迫使设计者选用更高耐压的整流器件,而高耐压器件通常伴随更高的导通电阻(RDS(on))和输出电容(Coss),直接制约了转换器效率的进一步提升。传统解决方案是在整流器两端并联电阻-电容-二极管(RCD)无源钳位电路,但这会将谐振能量以热的形式耗散掉,牺牲了效率。

引言

相移全桥(PSFB)转换器因其能在初级侧开关管上实现软开关(降低开关损耗),成为高功率应用(如服务器电源、工业电源、通信电源)的主流拓扑。然而,传统的PSFB存在一个显著痛点:变压器漏感(Lr)与输出整流器(特别是同步整流管MOSFET)的寄生电容(Coss)谐振,会导致次级侧产生严重的电压振铃和尖峰。此尖峰电压理论上可达 2 × VIN × (NS/NP),迫使设计者选用更高耐压的整流器件,而高耐压器件通常伴随更高的导通电阻(RDS(on))和输出电容(Coss),直接制约了转换器效率的进一步提升。传统解决方案是在整流器两端并联电阻-电容-二极管(RCD)无源钳位电路,但这会将谐振能量以热的形式耗散掉,牺牲了效率。

图 1. 具有无源钳位和主要波形的 PSFB 功率级

有源钳位:高效率的解决之道

为了克服无源钳位的效率瓶颈,有源钳位(Active Clamp)技术被引入PSFB转换器。其核心思想是将原本耗散在电阻上的能量进行无损循环利用,同时有效抑制整流器电压应力。

工作原理

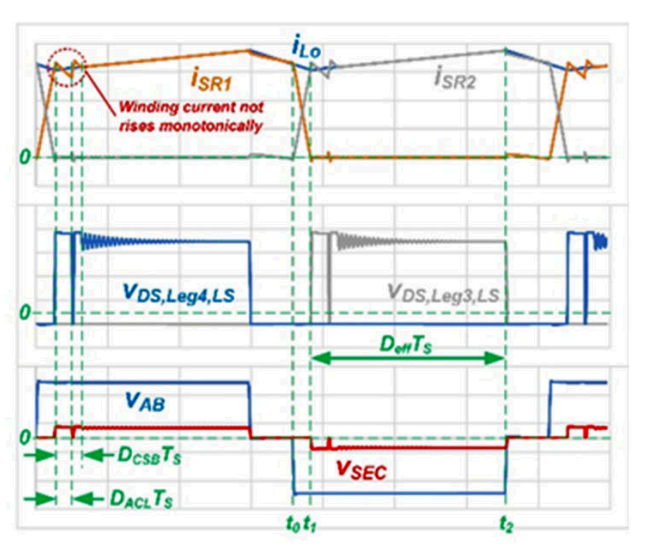

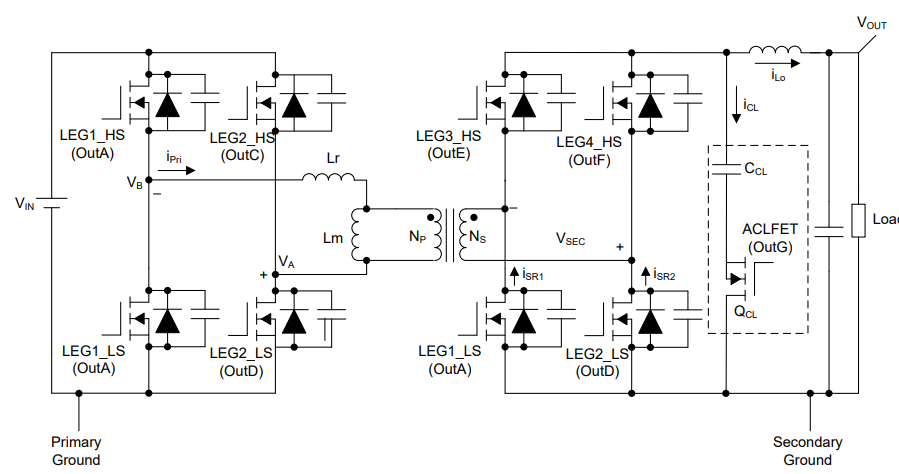

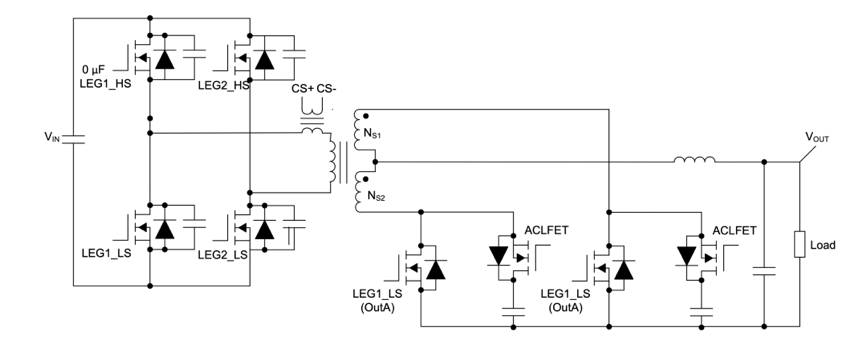

如图2所示,有源钳位支路由一个钳位电容(CCL)和一个钳位开关管(QCL, 通常为MOSFET)串联组成,放置在输出滤波电感(Lo)之前、变压器次级绕组之后。

1. 钳位动作: 当次级绕组电压(VSEC)由于谐振试图超过目标钳位电压(-VCL)时,QCL的体二极管(或在其导通时)会导通,将VSEC和整流器(SR1, SR2)两端的电压钳位在-VCL附近。通过合理设计(CCL足够大,其电压纹波小),VCL可稳定在VIN × (NS/NP)左右。这意味着整流器承受的最大电压应力从2 × VIN × (NS/NP)显著降低到VIN × (NS/NP),允许选用更低耐压、更低RDS(on)和更低Coss的MOSFET作为同步整流管(SR),这是提升效率的关键一步。

图 2. 具有有源钳位和主要波形的 PSFB 功率级

2. 能量循环: 与RCD不同,有源钳位电路本身不消耗能量。在谐振过程中,能量在漏感Lr、SR的Coss和钳位电容CCL之间交换。当QCL在其体二极管导通后适时开通(实现QCL的零电压开关 - ZVS),能量得以在谐振回路中循环,而非被电阻耗散。

3. 工作波形: 在占空比丢失(Dead Time)期间,VSEC=0,SR进行换流。此时,输出电感电流(iLo)主要通过导通的SR续流。有源钳位支路电流(iCL)在此阶段开始流动并达到峰值(iCL,peak),其值受SR的Coss和漏感Lr影响显著(公式参考原文公式5-7)。随后,当初级侧能量再次传输到次级时,CCL中储存的部分能量也会参与为输出电感Lo充电。

设计关键考量与挑战

实现高效可靠的有源钳位PSFB,需关注以下核心点:

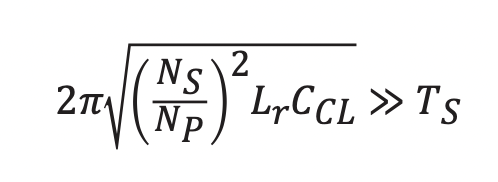

1. CCL容值选择: 为确保低电压纹波和有效钳位,需选择足够大的CCL。设计准则通常要求由Lr和CCL构成的LC谐振周期远大于开关周期(TS),即满足 2π√(Lr × CCL) >> TS (参考原文公式1)。这保证了在开关周期内,VCL基本保持恒定。该周期远长于由方程式 1 表示的开关周期 (TS):

方程式1

2. QCL驱动时序:

● 开通时机: 必须在占空比丢失阶段结束 之后 开通QCL,以防止CCL能量倒灌回初级侧。同时,为了最大化利用体二极管导通实现ZVS,应在体二极管导通期间(或刚导通后)开通QCL。

● 导通时间: 较长的QCL导通时间能更好地维持VCL稳定,进一步降低SR应力,但会增加QCL的导通损耗(RMS电流增大)。需要在电压应力和效率之间做优化折衷。

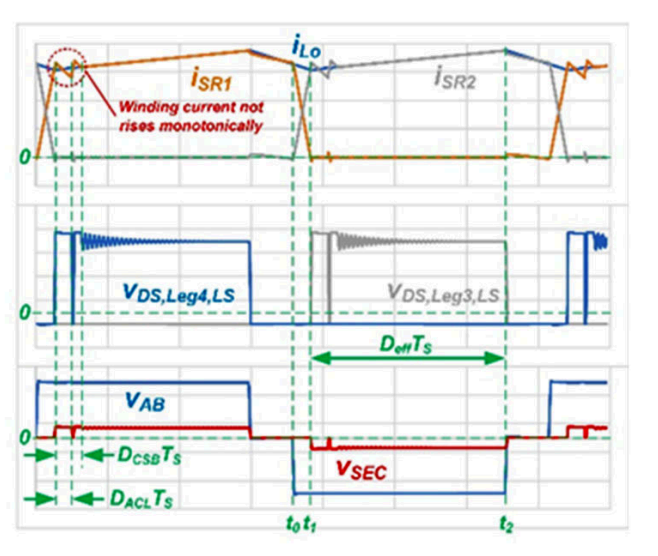

图 3. 有源钳位电流传导周期的主要波形

3. SR MOSFET选择: 低Coss的SR MOSFET至关重要! 较低的Coss不仅直接降低了整流器本身的开关损耗和电压应力尖峰(在无钳位或钳位未完全生效的瞬间),更重要的是它能显著减小有源钳位支路的峰值电流(iCL,peak)和有效值(RMS)电流(参考原文公式5-7),从而降低QCL的导通损耗和CCL的损耗,整体提升效率。选用低RDS(on)的器件则进一步降低导通损耗。

假设 VCL 为常量且 Lm= ∞,则方程式 2 将占空比损耗周期(VSEC=0 且 iSR1 和 iSR2 正在换流的周期)期间的整流器电流变化率表示为:

方程式 2

其中 VLr 是 Lr 两端的电压。

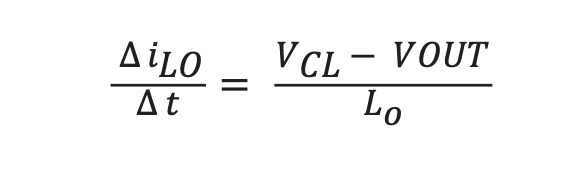

方程式 3 计算输出电感器电流的变化率:

方程式 3

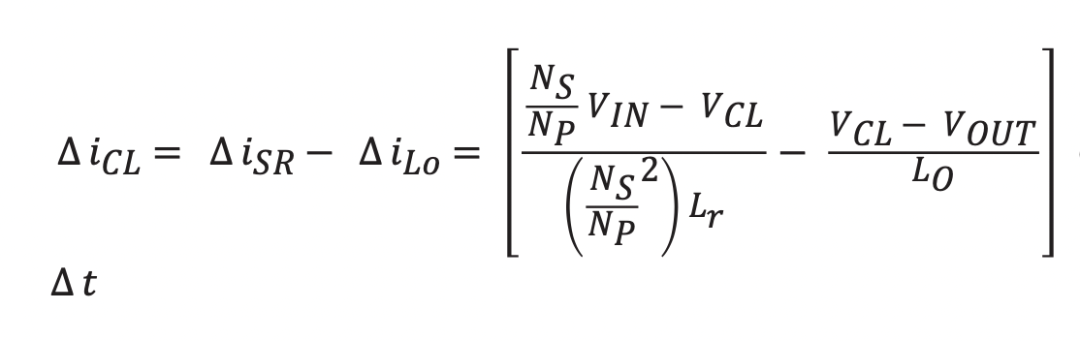

利用方程式 2 和方程式 3 以及基尔霍夫电流定律,方程式 4 计算有源钳位电流的变化率:

方程式 4

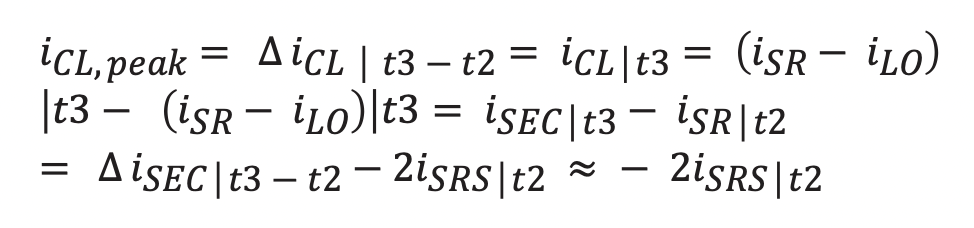

由于 VCL≈VIN×NS/NP,因此您只需将总有源钳位支路传导时间作为方程式 4 中的 Δt,即可求解 ΔiCL。但是, 您仍需要知道 iCL 的峰值,才能计算 iCL 均方根 (RMS) 值。如图 3 所示,如果在时间 t2 时 iSEC = iLo (在将 Coss 充电至 VCL 后),而在时间 t3 时 iSEC = iSR (开始对 CCL 充电),则方程式 5 可推导出 iCL,peak 值为:

方程式 4

由于 VCL≈VIN×NS/NP,因此您只需将总有源钳位支路传导时间作为方程式 4 中的 Δt,即可求解 ΔiCL。但是, 您仍需要知道 iCL 的峰值,才能计算 iCL 均方根 (RMS) 值。如图 3 所示,如果在时间 t2 时 iSEC = iLo (在将 Coss 充电至 VCL 后),而在时间 t3 时 iSEC = iSR (开始对 CCL 充电),则方程式 5 可推导出 iCL,peak 值为:

方程式 5

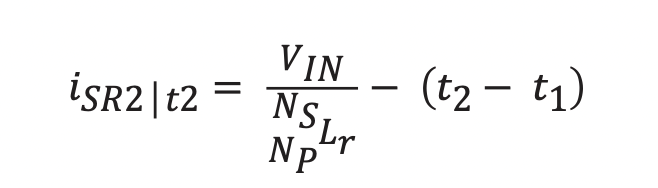

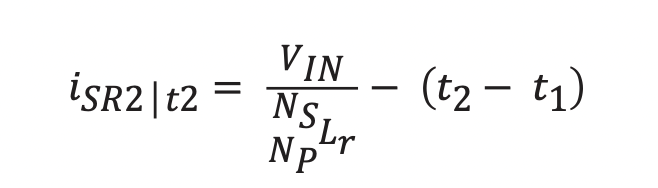

通过方程式 6 将 t2处的 iSR2 值推导为:

方程式 6

假设 iSR2 电流从 t0 到 t2 的递减速率相同,则方程式 7 推导出 t2-t1 的持续时间为:

方程式 7

4. 控制策略的挑战(峰值电流模式): 引入有源钳位后,变压器次级电流(iSEC)在有效占空比(Deff)期间不再是单调上升的(因为CCL也参与供能)。这使得传统的、依赖初级或变压器绕组(初级侧)峰值电流检测的峰值电流模式控制变得复杂,因为检测到的电流峰值不能直接、线性地反映实际传输的能量或所需的占空比。

● 解决方案: 为了维持可控性,需确保在整个工作范围内(特别是轻载时),有效占空比时间(Deff * TS)大于完成电流-秒平衡(Current-Second Balance)所需的时间(DCSB * TS)。一种有效的实践是采用基于负载电流的降频(Frequency Foldback)控制。在轻载或空载时降低开关频率,使得即使在较小的Deff下,也能满足 Deff * TS > DCSB * TS 的条件,保证峰值电流检测的有效性和系统的稳定性。同时,固定或优化控制QCL的开通时间。

应用实例与性能验证

有源钳位技术具有拓扑普适性,不仅适用于全桥整流,同样适用于中心抽头(Center-Tapped)或倍流(Current Doubler)整流结构。

● 案例: 在德州仪器(TI)发布的3kW相移全桥参考设计(功率密度 > 270W/in³)中,成功应用了中心抽头整流器搭配双有源钳位支路(结构参考原文图4)。

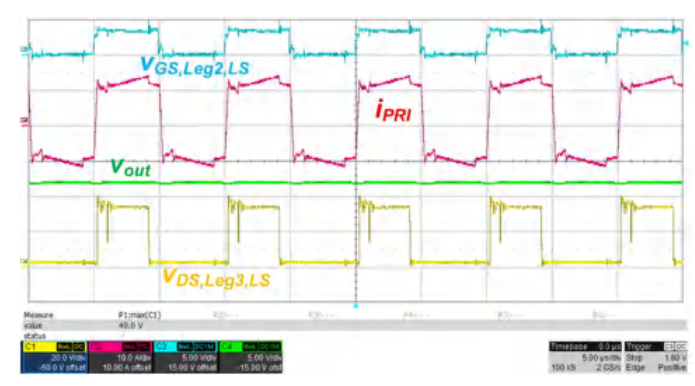

● 实测结果(参考原文图5): 在输入电压400V,输出12V/250A(即3kW)的满载条件下:

● 同步整流管(SR)上的电压应力被有效钳制在40V以下(远低于理论最大值)。

● 有源钳位电路本身引入的额外损耗极低(可忽略不计),主要损耗来自QCL和SR的导通损耗。

● 该设计实现了极高的转换效率,充分体现了有源钳位在降低应力、减少损耗方面的巨大优势。

图 4. 中心抽头整流器上带有有源缓冲器的 PSFB 转换器

图 5. 具有中心抽头整流器和有源缓冲器的PSFB 转换器在12V/3kW 输出下的稳态波形

总结

在PSFB转换器中采用有源钳位技术是提升效率和功率密度的有效途径。它通过无损能量循环,将输出整流器的电压应力有效钳位至约VIN × (NS/NP),使得采用低耐压、低损耗的同步整流MOSFET成为可能,显著降低了导通损耗和潜在的开关损耗。虽然其对次级电流波形的影响给峰值电流模式控制带来挑战,但通过合理选择器件(重点:低Coss的SR FET)、精心设计钳位电容(CCL)、优化钳位开关(QCL)驱动时序(确保ZVS并避免能量倒灌)以及实施降频控制策略,这些挑战可以被成功克服。实验结果证明,有源钳位PSFB能在高功率(如3kW)、高电流(如250A)输出下,实现优异的电压应力抑制和极高的整体转换效率,为下一代高效高密度电源设计提供了强有力的技术支撑。

推荐阅读:

DigiKey B站频道火出圈:粉丝破10万大关,好礼送不停

IOTE 2025深圳物联网展:七大科技领域融合,重塑AIoT产业生态

9.9元抢500元超值观展礼包!深圳智能工业展早鸟福利限时开抢