【导读】想要降低系统中增加的噪声,必须降低电压噪声。常用方法——并联放置多个缓冲器可降低电压噪声。但是,该方法会使偏置电流、电流噪声、输入电容,统统提高,这时,你需要一款4通道JFET缓冲放大器!

缓冲器是什么?

许多电子电路需要利用一个器件来将不同的电路隔离或分离开。这种特殊器件称为缓冲器。缓冲器是单位增益放大器,具有极高输入电阻和极低输出电阻。这意味着可以将缓冲器模拟为一个增益为1的压控电压源。缓冲器具有几乎无限大的输入电阻,因而不存在负载效应,故VIN = VOUT。此外,缓冲器的输出电压对负载电阻不敏感,因为理想缓冲器的输出电阻基本上为零。将单位增益缓冲器放置在数模转换器(DAC)和负载之间,可以轻松解决负载效应问题。

缓冲器噪声计算

给系统添加单位增益缓冲器时,务必不要影响精度和性能。最重要的一点是计算增加的噪声:

其中:

en = 缓冲器输入电压噪声密度

in = 缓冲器输入电流噪声密度

f = 器件输入带宽(Hz)

JFET降噪原理

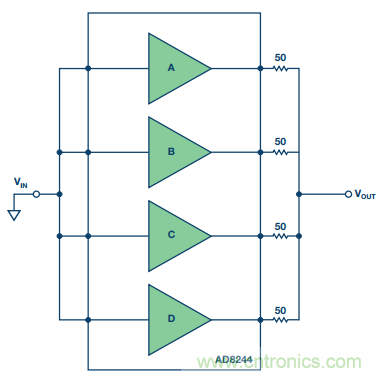

在图1所示电路中,各通道的电流噪声极低(0.8 fA/√Hz);相比之下,电压噪声则有13 nV/√Hz。因此,要降低系统中增加的噪声,必须降低此电压噪声。并联放置多个缓冲器可降低电压噪声。例如,两个缓冲器并联可将电压噪声降低√2,所有四个缓冲器并联相当于一个噪声减半的缓冲器。

图1. 新型低噪声缓冲器AD8244

这种方法的缺点是偏置电流、电流噪声和输入电容提高,但在本例中,这些效应可忽略不计。在输出之间放置一个50 Ω之类的小电阻,可防止各输出之间的细微差异引起的额外电流流动。对于对功耗不太敏感的应用,可以省去这些50 Ω电阻以提高可用输出电流。图1所示电路是缓冲放大器的一种新型配置,能将电压噪声减半。

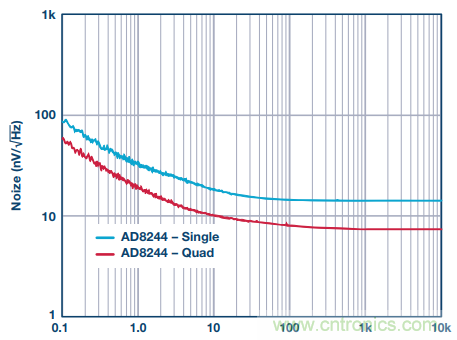

图2比较了普通单通道缓冲器和有四个并联通道的新型缓冲器AD8244的噪声性能。

图2. 新型缓冲器AD8244的性能:噪声仅为普通缓冲器的一半

AD8244是一款四通道、JFET输入、单位增益缓冲器,具有远超预期的高性能。其最大偏置电流为2 pA,电流噪声接近于零,输入阻抗为10 TΩ,因此即使源阻抗为MΩ级别,也几乎不产生任何误差。该器件具有低电压噪声、宽电源范围和高精度特性,而且非常灵活,足以为任何需要单位增益缓冲器(甚至低源电阻)的应用提供高性能。

很多传统运算放大器都将电源引脚排列在同相输入引脚旁边。 保护走线必须从这些引脚之间穿过,以避免漏电流远大于FET输入运算放大器的偏置电流。在DIP乃至SOIC等大型封装内,保护走线可以在引脚间穿过;但是,很多现代应用不允许这些封装消耗过多的面积。AD8244具有独特的引脚排列可以解决这个问题,它在物理上将高阻抗输入与低阻抗电源以及其它缓冲器的输出相隔离。 这种配置简化了保护功能,同时缩小了电路板空间,允许在同一个设计中达到高性能和高密度。

AD8244专门针对解决缓冲器相关问题而设计。 它具有紧密的通道间匹配,允许AD8244的通道用于差分信号链,且误差极小。 该器件具有低电压噪声、宽电源范围和高精度特性,因此还非常灵活,足为任意需要单位增益缓冲器(甚至低源电阻)的应用提供高性能。

推荐阅读: