【导读】三星电子传来关键突破信号。据韩国媒体TheElec报道,其第七代高带宽内存产品HBM4E已正式迈入基础芯片后端设计阶段,这一里程碑式进展标志着整体研发进程过半,量产时间表锁定2027年。作为HBM模块的“控制中枢”,基础芯片的设计进程直接决定产品性能上限,而三星此次不仅剑指3.25 TB/s总带宽、两倍于HBM3E的能效等硬核指标,更以4纳米工艺、双轨研发策略构建竞争壁垒,为全球AI基础设施的存储效率革命注入新动能,也让这场由三星、SK海力士、美光主导的技术竞赛进入更关键的攻坚期。

据悉,HBM4E的基础芯片目前已完成寄存器传输级(RTL)逻辑设计,正进行物理电路的布局与布线(即后端设计)。这一阶段通常占芯片设计总周期的60%至70%,完成后将进入流片(tape-out)准备,由代工厂启动试产。

作为HBM模块的“控制中枢”,基础芯片不仅负责管理数据读写速度,还承担对上方堆叠DRAM的错误校正(ECC),直接决定整颗HBM的性能、稳定性与能效。

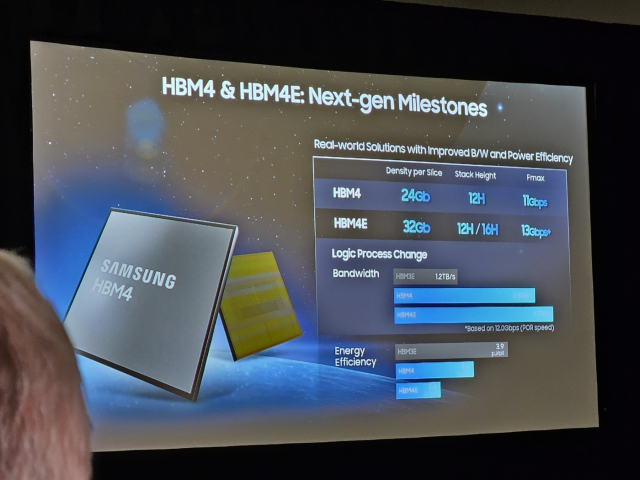

根据此前的信息,三星为HBM4E设定了技术指标:总带宽目标高达3.25 TB/s,较当前主流的HBM3E提升约2.5倍;每针脚数据速率突破13 Gbps;同时维持2,048个I/O接口以确保兼容性。同时,其能效目标是HBM3E的两倍以上。这对功耗敏感的数据中心和AI训练集群至关重要。

为加速商业化进程,三星已向供应链发出明确信号:要求供应商在2026年3月前提交配套材料与设备供应计划。公司内部更制定了覆盖HBM4、HBM4E到HBM5(预计2029年推出)的完整路线图,并同步运营两个研发团队——一个专注标准品,另一个专攻定制方案,形成“双轨并行”策略。

TheElec称,三星计划在其自有的4纳米FinFET工艺节点上制造HBM4E的基础芯片,并由存储器接口专家林大贤(Daihyun Lim)领衔I/O设计。林大贤曾任职IBM与GlobalFoundries,2023年加入三星,其经验被视为攻克高速信号完整性难题的关键。

总结

三星HBM4E进入基础芯片后端设计阶段,既是其技术路线图的关键跨越,也印证了全球HBM产业向高带宽、优能效迭代的趋势。依托4纳米FinFET工艺、专家团队攻坚及全链条布局,三星全力抢占AI存储赛道。当前HBM市场短缺将持续至2028年,AI大模型需求激增背景下,HBM4E进展深刻影响全球AI服务器供应链格局。随着2026年供应链配套落地及流片试产推进,三星能否凭此产品重塑竞争格局、为2027年量产及HBM5研发铺路,备受行业关注,其技术突破也将助力AI基础设施向高效低耗升级。