【导读】当前的半导体产业,大多要求尺寸、功耗、重量、性能。在GSPS领域的数位类比转换器技术(DAC)尤以性能为关键。本文主要阐述了元件的匹配和互连,在选择变压器及连接配置技巧时的规格,以及如何在GHZ级区域作业的DAC实现宽频平滑阻抗转换。

为了提供更高的清晰度,一般都认为高频是指超过1GHz的频率,而高速要超过1GSPS的速度;但更重要的是,终端用户可能会在DAC之后整合一个放大器,因此可用讯号便不那么依赖于讯号电平,而是更加地取决于杂讯和真实性。本文将讨论匹配元件及其互连,并在选择变压器或「平衡-不平衡转换器」(巴伦;Balun)以及连接配置技巧时重点关注的关键规格。最后,还将提供一些思路和最佳化技巧,说明在GHz级区域作业的DAC如何实现宽频平滑阻抗转换。

DAC的背景

DAC用途广泛,最常见的用途包括商业和军事通讯中的高频复杂波形产生、无线基础设施、自动测试设备(ATE),以及雷达和军用干扰电子产品。系统架构师找到合适的DAC后,必须考虑输出匹配网路,以保持讯号结构。元件选型和拓扑较从前更为重要,因为GSPS DAC应用要求工作在超级奈奎斯特(Nyquist)频率下,此时所需的频谱讯息位于第二、第叁或第四奈奎斯特区。

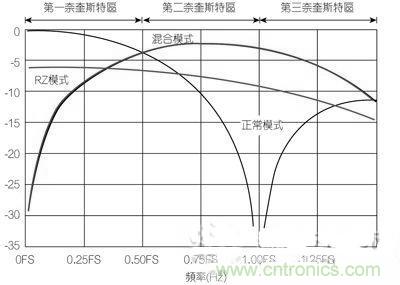

首先探讨DAC的角色及其于讯号链中的位置。DAC的作用很像讯号产生器,它能在中心频率(Fc)範围内为复杂波形提供单音。以前,Fc最大值位于第一奈奎斯特区中,或者是採样频率的一半。较新的DAC设计具有内部时脉倍频器,能有效地倍增第一奈奎斯特区;可将其称为「混频模式」操作。使用混频模式的DAC自然输出频率响应具有sinx/e^(x^2 ) 曲线的形状,如图1所示。

系统架构师可参考产品资料手册,了解元件性能。很多时候,诸如功率水平和无杂散动态範围(SFDR)等性能参数会给出多种频率下的数值。明智的系统设计人员可将同一个DAC应用于上述的超奈奎斯特区中。值得注意的是,在较高频率下(或较高区域中)预期输出电平将会低得多,因此很多讯号链会在DAC之后整合一个额外的增益模组或驱动放大器,以补偿该损耗。

图1:DAC Sinx/x输出频率响应与混频模式的关係。

元件考量:选择输出巴伦

只有终端用户设计和测得的最佳性能GSPS DAC才是好元件。为了使高品质DAC发挥最佳性能,应当只选用最好的元件。特别是关键电路,必须在一开始就决定好。资料手册上的DAC性能是否提供足够的输出功率?是否需要主动元件?讯号鍊是否需要从DAC差分输出传送至单端环境?是否需要用到变压器或巴伦?巴伦的合适阻抗比是多少?本文将重点讨论巴伦或变压器的使用。

选择巴伦时,应仔细考虑相位和幅度不平衡。阻抗比(即电压增益)、频宽、插入损耗和回损同样也是重要的性能考虑因素。採用巴伦进行设计并不总是简单明瞭。例如,巴伦的特性随频率而改变,这会使塬有预期蒙上阴影。有些巴伦对接地、佈局佈线和中心抽头耦合敏感。

系统设计人员不应完全根据巴伦资料手册上的性能作为元件选择的唯一基础。经验在这裡能够发挥巨大作用:存在PCB寄生效应时,巴伦以新的形式构成外部匹配网路;转换器的内部阻抗(负载)同样成为等式的一部分。

使用单个巴伦或多个巴伦拓扑时,还需要注意的一点是,佈局对于相位不平衡同样具有重要作用。为了在高频下保持最佳性能,佈局应尽可能对称。否则,走线轻微失配可能使採用巴伦的前端设计变得毫无用处,甚至使动态範围受限。

[page]

输出匹配

依赖频率的元件将会始终限制频宽,如并联电容和串联电感。也就是说,考虑最佳化而非匹配,可能更为有效。目前,巴伦的超宽频宽几乎不可能「配合」多倍频程频谱範围。对以上参数的最佳化则要求对系统的终端应用有深入的瞭解。例如,电路是否需要提供最大功率传输,而较少考虑SFDR?或者是否需要最高线性度设计,同时突出SNR和SFDR而较少考虑DAC的输出驱动强度?这意味着在应用中,应当权衡每个参数的重要性。

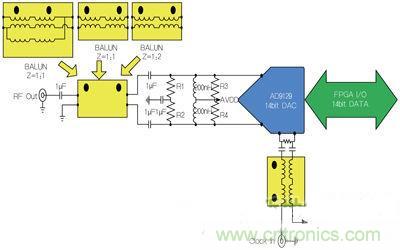

图2:AD9129 DAC输出前端功能框方块图

本例中,如图2所示为AD9129 GSPS DAC输出网路。该网路中的每个电阻和巴伦都可改变,然而随着每个电阻值的变化,性能参数也会如表1所示发生变化。

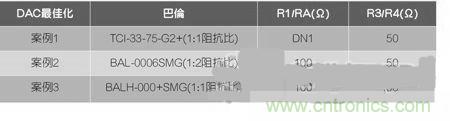

表1:数据定义的几种应用案例。

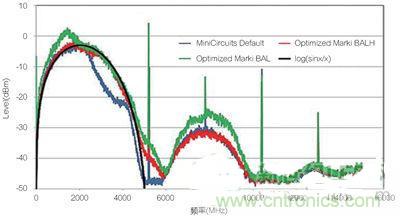

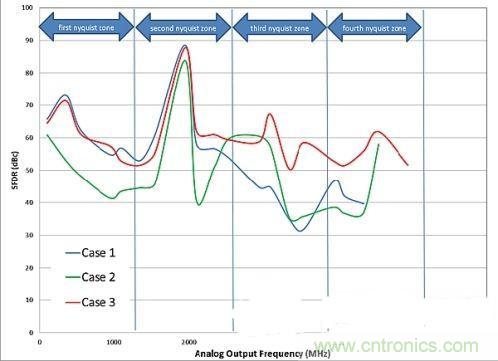

读者必须注意的是最佳元件值之间的差异非常小。巴伦元件具有最大的变化值。图3中的数据显示DAC宽频杂讯输出模式的最佳化;DAC只是在全部可用频谱频宽中产生讯号音。

图3:宽频杂讯模式中的DAC性能

第一个案例显示第一奈奎斯特区的可用功率下降,而第二、第叁和第四奈奎斯特区中极有可能出现混叠讯号音。案例2显示第一和第二奈奎斯特区中的输出电平增加,以及较高奈奎斯特区中的可用功率下降。最后,案例3为最佳情况,看上去在第一和第二奈奎斯特区具有良好的输出功率,同时相比情形1,区域3和4中的可用功率保持在最低水平。

图4:SFDR性能对比

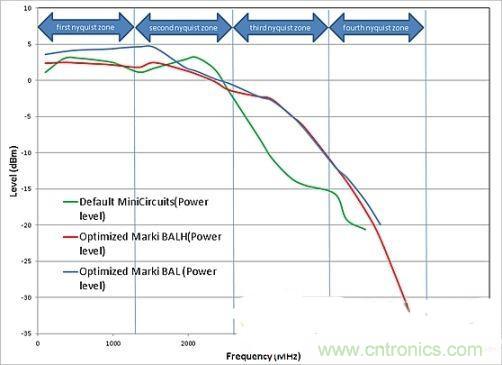

图4和5显示DAC为单音模式时的记录数据。图5显示多个奈奎斯特区中不同频率的输出功率水平。图4显示各种情形与DAC输出频率下的SFDR。读者应当对参数规划的权衡取捨有一个更全面的了解,因为随着设计过程的展开,必须理解这些参数并为其实现最佳化。显然,案例1可以透过更换为频宽更宽的巴伦解决方案加以改善,即案例2。在第二奈奎斯特区获得更高的功率水平和更佳的SFDR。此外,案例3中採用1:2宽频巴伦,使改善后的功率水平得能够加以保持,同时进一步改进系统的SFDR。其它重要发现:在1900MHz附近存在SFDR的「最有效点」。该性能独立于输出元件,这是因为DAC存在内部阻抗。

图5:输出功率水平对比

相关阅读: