【导读】在电子系统的时序架构中,晶体振荡器(晶振)与实时时钟芯片(RTC)构成精准计时的基础支撑。二者虽协同工作,却存在本质差异:晶振是频率生成的物理核心,而RTC是时间管理的逻辑中枢。据IEEE 1950.1标准测试数据,晶振频率稳定性可达±0.5ppm(如EPSON SG-210),而RTC芯片通过温度补偿算法将计时误差压缩至±2ppm(如MAXIM DS3231),共同保障从5G基站到智能电表的全局时间同步。

在电子系统的时序架构中,晶体振荡器(晶振)与实时时钟芯片(RTC)构成精准计时的基础支撑。二者虽协同工作,却存在本质差异:晶振是频率生成的物理核心,而RTC是时间管理的逻辑中枢。据IEEE 1950.1标准测试数据,晶振频率稳定性可达±0.5ppm(如EPSON SG-210),而RTC芯片通过温度补偿算法将计时误差压缩至±2ppm(如MAXIM DS3231),共同保障从5G基站到智能电表的全局时间同步。

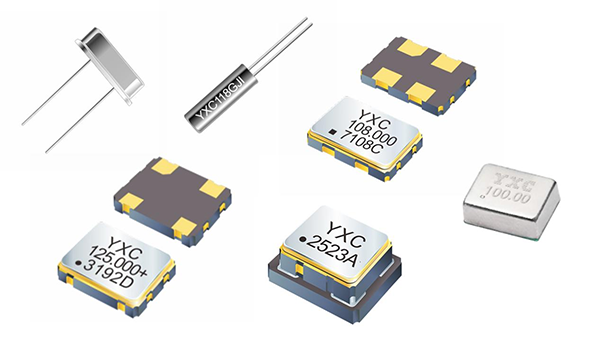

一、晶振:原子级精度的频率源

物理原理

晶振利用石英晶体的压电谐振效应,当交变电压施加于晶片(常用AT切割角±35°)时,晶体以固有频率产生机械振动。该频率由晶片厚度决定(公式: ,k为材料常数,d为厚度),例如32.768kHz晶片厚度仅2.18mm。

,k为材料常数,d为厚度),例如32.768kHz晶片厚度仅2.18mm。

核心优势与局限

数据来源:IEEE Transactions on Ultrasonics(2023)

二、RTC芯片:时间管理的中枢系统

架构解析

RTC芯片本质是集成化时间处理器,包含三大功能模块:

1. 信号输入:外接32.768kHz晶振作为基准源

2. 分频链:15级二分频(215=327682 15 =32768)生成1Hz秒脉冲

3.时间寄存器:二进制转BCD码输出日历时间

核心价值突破

●超低功耗运行:在备份模式下,MAXIM DS1337U功耗仅300nA,十年不换电池

●温度补偿技术:内置温度传感器+数字补偿算法(如NXP PCF8523),-40℃~85℃全温区误差<±2ppm

●事件记录能力:支持64字节RAM存储时间戳(如瑞萨RX8111CE),满足IEC 62053电能表标准

三、系统协同与本质差异

协同工作模型

晶振(物理层) → 生成32.768kHz基准频率 → RTC芯片(逻辑层) → 分频+日历计算 → 输出时间数据

关键差异对比

*数据来源:Digi-Key 2024年报价及厂商数据手册*

四、选型要则与场景适配

晶振选型关键

●频率精度:消费电子选±20ppm,基站要求±0.5ppm

●负载电容匹配:偏差>5pF将导致频率偏移2%

●封装抗振性:汽车电子首选金属封装(如KYOCERA KC2520K)

RTC芯片选型策略

●功耗敏感型:选nA级备份电流型号(ABLIC S-35390A)

●宽温应用:内置温补模块(Microchip MCP7940N)

●事件记录需求:扩展RAM型(EPSON RX8900CE)

国产替代进展

●晶振领域:泰晶科技(TX3225)温漂控制达±5ppm

●RTC芯片:贝特莱(BL5372)功耗0.4μA,但温补精度仅±5ppm(较MAXIM差距2.5倍)

结语

晶振与RTC构成电子设备的“心跳”与“生物钟”。晶振以物理谐振保障频率根基,RTC凭数字逻辑实现时间演进。在工业4.0时代,二者协同精度直接决定系统可靠性——5G基站需ns级时间同步,智能电网依赖日误差<0.5秒的计时。未来随着MEMS振荡器与原子钟技术下沉,时间基准系统将向“更高精度、更低功耗、更强抗扰”三维突破。

推荐阅读:

光伏充电控制器升级首选?TI GaN 的高效小型化低成本之道